Pesquisadores doPolitécnico de Milão desenvolveram um novo chip inteligente capaz de reduzir drasticamente o consumo de energia e ao mesmo tempo acelerar o processamento de dados massivos. Ao deslocalizar o cálculo diretamente na memória, esse componente abala a arquitetura tradicional dos computadores.

A corrida pelo poder computacional, impulsionada pela inteligência artificial, está a atingir um muro energético. Hoje, a constante movimentação de dados entre memória e processador é o principal obstáculo à eficiência do sistema.

Foi esse “gargalo” que a equipe da professora Daniele Ielmini decidiu atacar com uma arquitetura de cálculo analógico in-memory.

Quebrando o gargalo de Von Neumann

A arquitetura clássica dos computadores baseia-se num princípio imutável: os dados fazem incessantes idas e vindas entre memória e processador. Isso é chamado de gargalo de Von Neumann. Esta transferência de informação é lenta e consome muita energia.

O chip italiano é uma virada de jogo. É baseado no conceito de Computação na memória. Num computador típico, os dados viajam constantemente entre a unidade de processamento e o armazenamento. Esse tráfego interno gera calor e retarda as operações.

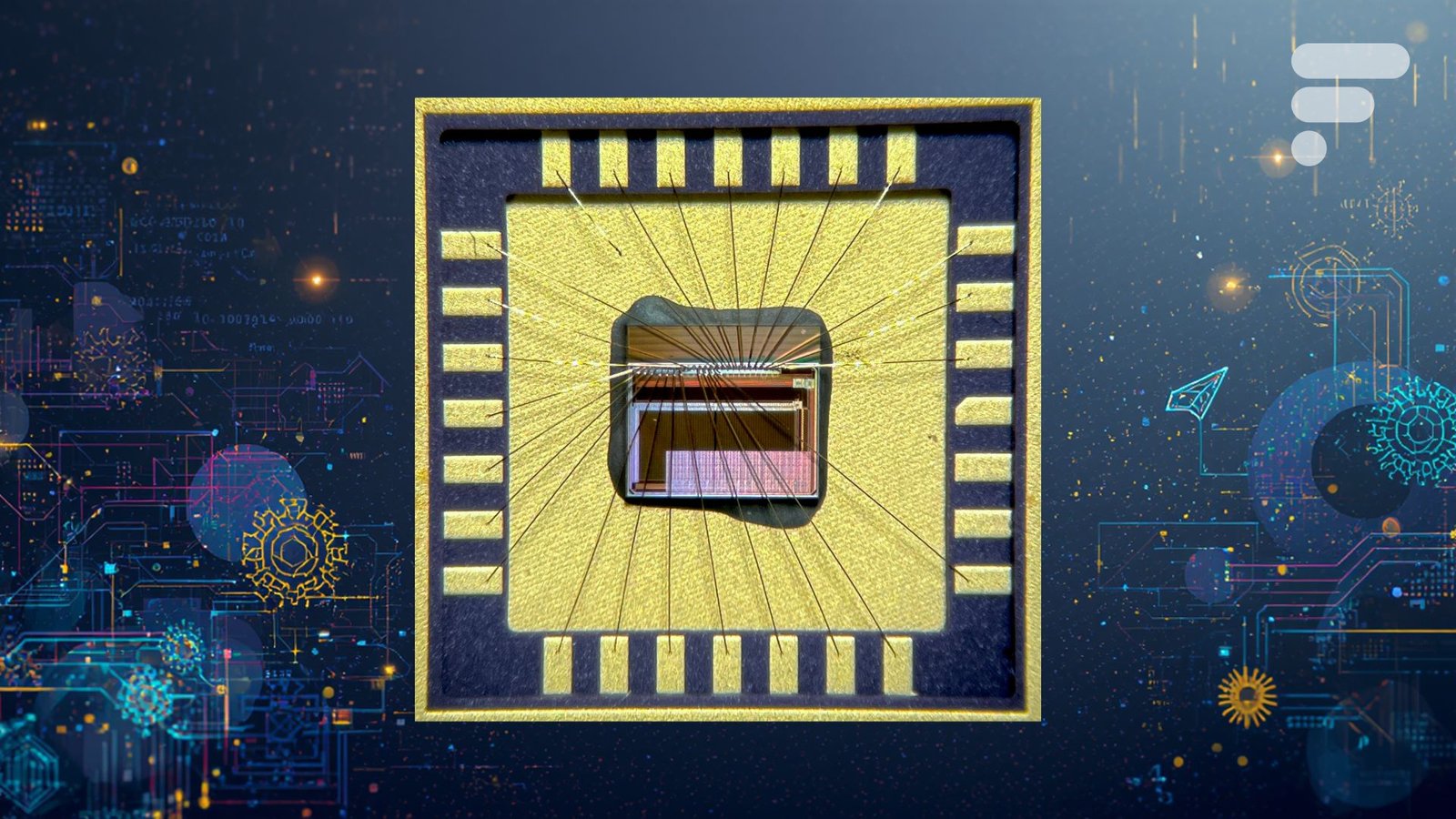

O novo dispositivo usa dois arrays 64×64 memórias resistivas programáveis. Esta estrutura de grade permite a realização de cálculos complexos sem nunca remover as informações da memória. “Ao eliminar este tráfego interno, os sistemas tornam-se mais rápidos e mais eficientes energeticamente”explicam os pesquisadores.

Ganhos de desempenho estonteantes

Os resultados preliminares são impressionantes. O tempo de cálculo cai para aproximadamente 100 nanossegundosum valor que permanece estável independentemente do tamanho do problema a ser resolvido.

Do lado da energia, o ganho é enorme. Segundo os pesquisadores, esta tecnologia requer 5.000 vezes menos energia do que computadores digitais de última geração para precisão equivalente.

Rumo a uma IA mais sustentável

O desafio deste projeto chamado ANIMAR (Analogue In-Memory computing with Advanced device TEchnology) é significativo: o treinamento de grandes modelos de linguagem atualmente consome volumes colossais de eletricidade.

Ao reduzir o consumo do servidor, este chip poderia limitar a explosão na demanda elétrica ligada à IA. Como um lembrete, esses data centers já pesam aproximadamente 1% do consumo global de eletricidade.

Prevê-se também equipar infraestruturas 5G e futuras redes 6G. Sua velocidade de processamento (100 ns) permitiria gerenciar fluxos massivos de dados com latência quase zero.

O mesmo vale para a robótica. O chip permite que cálculos complexos sejam realizados localmente, sem depender da nuvem. Este é um trunfo importante para robôs e veículos autônomos que exigem capacidade de resposta imediata.

Em última análise, esta inovação milanesa oferece uma alternativa credível para a computação de alto desempenho (HPC) e a IA sustentável.